## JOURNAL OF MECHANICS OF CONTINUA AND MATHEMATICAL SCIENCES

www.journalimcms.org

ISSN (Online): 2454-7190 Vol.-14, No.-5, September - October (2019) pp 98-110 ISSN (Print) 0973-8975

# All-Optical Logic Gates Based on Graphene Interferometric Waveguide

### Hassan FalahFakhruldeen<sup>1, \*</sup>, TahreerSafa'a Mansour <sup>2</sup>, Yousif I. Hammadi<sup>3</sup>

<sup>1,2,3</sup> Institute of Laser for Postgraduate Studies, University of Baghdad, Baghdad, Iraq

<sup>1</sup> Computer Technical Engineering Department, Collage of Technical Engineering, TheIslamic University, Najaf, Iraq

\*Corresponding author Hassan FalahFakhruldeen

E-mail: hassan.fakhruldeen@iunajaf.edu.iq

http://doi.org/10.26782/jmcms.2019.10.00008

#### **Abstract**

Novel types of all-optical logic gates based on graphene surface plasmonpolaritons (SSPs) are proposed in this study by utilizing linear constructive and destructive interferences among SSP waves in spatially separated graphene sheets. The realized logic gates are OR, AND, and XOR gates. The suggested transmission value threshold between the two states logic 0 and logic 1 is 0.5. Small modification in the structure has been conducted to implement the XOR gate with the same wavelength for all the proposed gates. The structure performance is measured on the basis of transmission efficiency of each implemented gate. The state of each input port can be easily controlled by switching the external gate voltage either ON or OFF. The function of the proposed gates can be achieved by modifying the chemical potential ( $\mu_c$ ), coupling length ( $L_c$ ), orinter spacing among the graphene sheets (d). These compact-sized logic gates are considered an important part in the integration of nanoscale photonic devices.

**Keywords**: Graphene, Surface plasmonpolaritons (SPPs), All-optical logic gate, Nanophotonic devices, Plasmonic logic gates.

#### I. Introduction

Graphene, as a new material type, has attracted considerable attention, especially in the research fields that focus on optoelectronics and other applications, due to its ideal properties [I]. The carrier mobility of graphene is approximately  $2 \times 10^5$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, which allows fabrication of ultra speed photonic components [II]. The episode light can be coupled firmly to graphene plates and afterward energize the graphene surface plasmonpolaritons (SPPs) over the surface of input ports [III-V].

The SPPs are the aggregate motion conduct of the free electrons on the material surface energized by outer sources. Owing to the remarkable specifications of SPPs, different types of sub wavelength photonic components have been scrutinized because these components can overcome the diffraction limit problem [VI, VII]. Traditional electronic logic gates have been imperative parts in signal processing and transmission systems. In any case, these gates have demonstrated a few drawbacks in various applications, such as latency failure, which decrease the reliability of devices. Nevertheless, all-optical logic gates can adapt to deformities, thereby attracting considerable attention [VIII-X]. Many all-optical gates can be actualized; several of them depend on optical interface [I, III-VIII], whereas others depend on nonlinear effects [IX-XII]. In Ref. [XIII], the cascaded gates in nanoscale photonic plasmon devices are exhibited, and the authors presume that the plasmonic NOR gate can be executed by utilizing cascaded OR and NOT logic gates. In Ref. [XIV], all-optical XOR, XNOR, and NOT gates in nanoscales are executed by utilizing plasmonic waveguides dependent on the linear interface among SSP modes. In Ref. [XV], the authors explore the optical properties of the graphene material depending on plasmonic waveguide that acts as AND and OR gates. Motivated by the recorded results of structured gates, the constructive or destructive coupling behavior will be utilized to realize different types of GSP-based logic gates. This article is organized as follows. The first part presents a concise introduction. The second part discusses the structure of the gates and the essential properties of graphene material. The third part comprehensively explores the different types of logic gates. The fourth part provides the conclusion.

#### II. Geometric structure and basic concepts

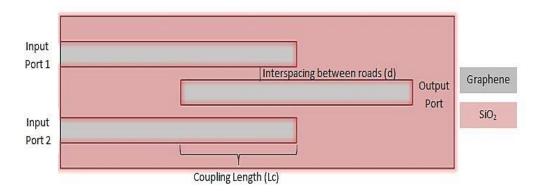

Considering the SPP coupling hypothesis of the graphene waveguide design shown in Fig. 1 and explored in [XVI], the SPP coupling coefficient ( $C_g$ ) among the graphene ports can be obtained as follows [XVII, XVIII]:

$$C_g = \frac{\beta_- - \beta_+}{2} \tag{1}$$

The coefficient of propagation constant ( $\beta$ +) is given as

$$\beta_{\pm} \approx k_{SPP} + \frac{2i \varepsilon_h k_0 / (\eta_0 \sigma_g) - k_p (1 \mp u_p)}{(1 \mp u_p) k_{SPP} / k_p \pm k_{SPP} d}$$

(2)

where  $k_p = (k_{spp}^2 - \varepsilon_h k_0^2)^{\frac{1}{2}}$ , and  $u_p = \exp(-k_p d)$  [XVII].  $\varepsilon_h$  is the dielectric permittivity of the channel where the isolated graphene layers are implanted, d is the space among the plates of graphene,  $\sigma_g$  is the surface conductivity of graphene,  $\eta_0 = 377\Omega$  (this value represents air impedance),  $k_0 = 2\pi/\lambda_0$  ( $\lambda_0$  is the wavelength of the episode light in air), and  $k_{SSP} = k_0 \left[ \varepsilon_h - 4\varepsilon_h^2/(\eta_0 \sigma_g)^2 \right]$  is the wave vector of SPPs supported by a graphene with a single layer [XVI]. The graphene material is usually represented as a two-dimensional material, and its tunability is

#### J. Mech. Cont. & Math. Sci., Vol.-14, No.-5, September-October (2019) pp 98-110

based on the complex surface conductivity, which is reduplicated by the intraband and interband contribution transitions [XIX] as  $\sigma = \sigma_{\text{intra}} + \sigma_{\text{inter}}$ . The two terms can respectively be represented as

$$\sigma_{\text{intra}}(\omega) = \frac{ie^2 \mu_c}{\pi \hbar^2 (\omega + i \tau^{-1})}, (3)$$

$$\sigma_{\text{inter}}\left(\omega\right) = \frac{ie^2}{\pi h^2} \ln\left(\frac{2 \mid \mu_c \mid -\left(\omega + i \tau^{-1}\right)\hbar}{2 \mid \mu_c \mid +\left(\omega + i \tau^{-1}\right)\hbar}\right).(4)$$

The conditions over (3) and (4) are legitimate only when  ${}^{k}{}_{B}T << \mid \mu_{c} \mid$ .  $\hbar$  represents the reduced Planck's constant, e is the electron charge,  $\mu_{c}$  is the chemical potential,  $\tau$  is the relaxation time constant,  $\omega$  is the radian angular frequency, T is the temperature in Kelvin, and  $k_{B}$  is the Boltzmann constant [XX].

Fig. 1. Graphene waveguide configuration

The coupling coefficient  $C_g$ , which is given in Eq. (1), can determine the coupling length  $L_c$  that gives the total mode propagated distance until the total energy is transferred from one waveguide to another, as given by [XVI, XXI]

$$L_c = \frac{\pi}{2\sqrt{2} |C_{\sigma}|} \tag{5}$$

#### III. All-Optical Logic Gates

The functions of the proposed gates can be realized by the constructive and destructive interferences between the input signals from the two input ports. For example, when input port 1 is disabled (OFF state) and input port 2 is active in (ON state) or vice versa, the destructive interference occurs between the input signals due to the phase difference that reduces the transmission. When both input ports are active (ON state), the constructive interference occurs between the input signals

[XXII]. In the proposed structure shown in Fig. 1, the graphene thickness is considered fixed with  $\varepsilon_g = 1 + i\,\sigma_g\,\eta_0\,/\,(k_0\,\Delta)\,[{\rm XVI}]$ . The graphene thickness ( $\Delta$ ) is considered = 1 nm to achieve high-speed software processing. Ref. [XX] indicates that the application of an incredibly high electric field is crucial to achieving the relentless task of this structure, which is not the best strategy. In view of Kubo's technique, a reverse connection exists between the applied wavelength and  $\mu_c$ , which is the real conductivity (associated with the loss coefficient). In this way, given that the proposed structure requires a low loss waveguide and minimal  $\mu_c$ ,  $10\,\mu m$  wavelength is applied; this value provides the ideal proportion of mode confinement/losses and enables the structure to work in a low chemical potential (»  $0.25~{\rm eV}$ ) [XX].

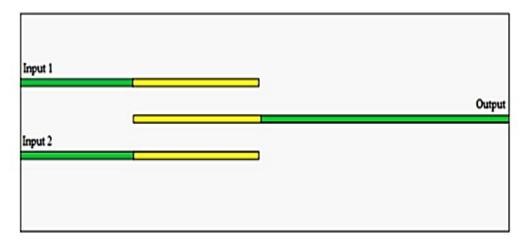

Fig.2. Interferometric device with two inputs and one output

The function of all-optical logic OR gate can be achieved from the proposed structure as shown above using the following structure parameters:  $L_c = 295.46$  nm,  $\mu_c = 0.229$  eV, d = 52 nm, and  $\varepsilon_h = 2.1$  (SiO<sub>2</sub> is used as a substraight).  $\lambda_0 = 10$  µm, T = 300 K, and  $\tau = 0.5$  ps (is rather conservative to feature the practical transport loss of graphene [XVI]).

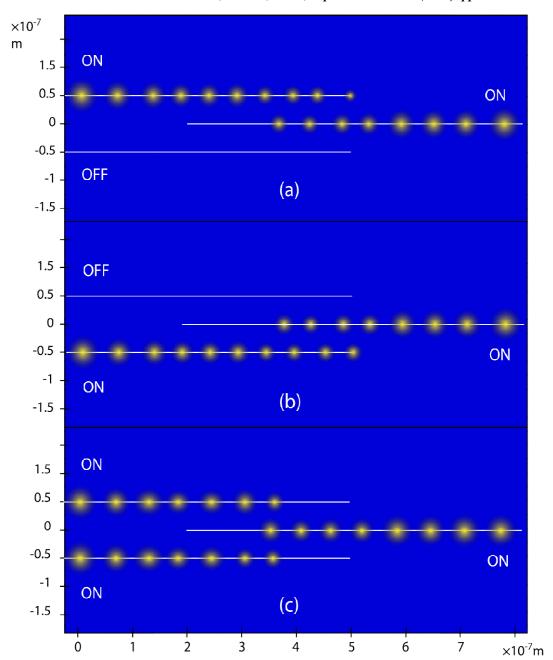

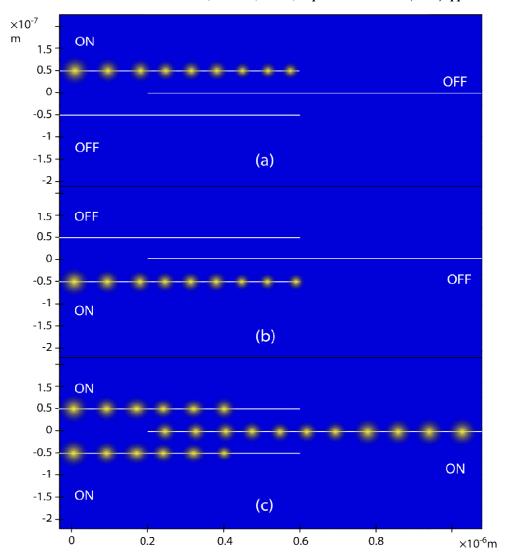

Fig. 3 shows the SPP distribution in the proposed device for different input states. Figs. 3a, 3b, and 3c show the results when only input port 1 is active (ON state), only input port 2 is active (ON state), and both ports are active (ON state), respectively.

Fig. 3. SPP mode distribution in the structure as logic OR gate with  $\mu_c$ = 0.229 eV,  $L_c$  = 295.46 nm, and d = 52 nm. Activation input state: (a) only input port 1 is active, (b) only input port 2 is active, and (c) both input ports are active.

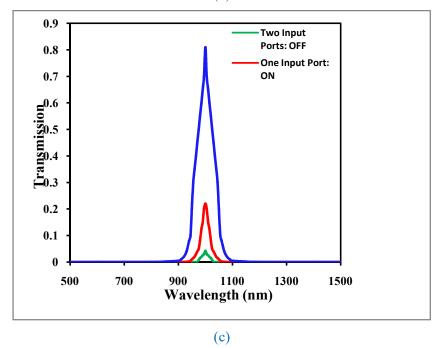

The transmission spectrum of the proposed OR gate structure is shown in Fig. 4c. The operation of the proposed OR gate is summarized in Table 1.

| Input |     | Output |

|-------|-----|--------|

| Α     | A B |        |

| 0     | 0   | 0      |

| 0     | 1   | 1      |

| 1     | 0   | 1      |

| 1     | 1   | 1      |

(b)

Fig. 4. (a) Symbol of a traditional electronic OR gate. (b) Truth table of OR gate. (c) Transmission efficiency of the proposed all-optical OR logic gate at different input states.

J. Mech. Cont. & Math. Sci., Vol.-14, No.-5, September-October (2019) pp 98-110

Table 1 Operation of the proposed OR gate structure.

| State<br>of<br>input<br>port 1 | State<br>of<br>input<br>port 2 | Activation of input port 1 | Activation of input port 2 | Transmission<br>efficiency | State<br>of<br>output<br>port | Activation of output port |

|--------------------------------|--------------------------------|----------------------------|----------------------------|----------------------------|-------------------------------|---------------------------|

| Logic 0                        | Logic<br>0                     | OFF                        | OFF                        | 0.42 %                     | Logic 0                       | OFF                       |

| Logic 0                        | Logic<br>1                     | OFF                        | ON                         | 22 %                       | Logic 1                       | ON                        |

| Logic 1                        | Logic<br>0                     | ON                         | OFF                        | 22 %                       | Logic 1                       | ON                        |

| Logic 1                        | Logic<br>1                     | ON                         | ON                         | 81 %                       | Logic 1                       | ON                        |

AND logic function can be obtained via the same structure shown in Fig. 1 using the following parameters:  $\mu_c = 0.25 \text{ eV}$ ,  $L_c = 409.37 \text{ nm}$ , and d = 60 nm. Fig. 5 shows the electrical field components  $E_y$  and SPP mode distribution in the device for different input logic states. Figs. 5a, 5b, and 5c show the results when only input port 1 is active (ON state), only input port 2 is active (ON state), and both input ports are active (ON state), respectively.

Fig. 5. SPP mode distribution in the structure as AND logic gate with  $\mu_c = 0.25$  eV,  $L_c = 409.37$  nm, and d = 60 nm. Input states: (a) only input port 1 is active, (b) only input port 2 is active, and (c) both input ports are active.

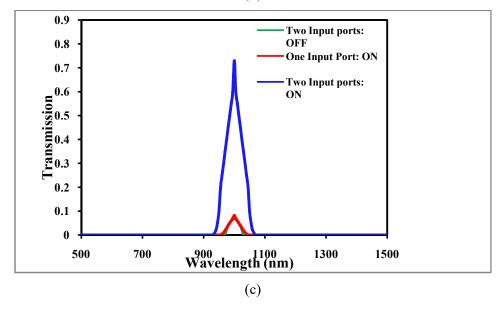

The transmission spectrum of the proposed AND logic gate is shown in Fig. 6c. The operation of the proposed AND gate is summarized in Table 2.

Copyright reserved © J. Mech. Cont.& Math. Sci. Hassan FalahFakhruldeen et al.

| Input |   | Output |  |

|-------|---|--------|--|

| А     | В | Y=A.B  |  |

| 0     | 0 | 0      |  |

| 0     | 1 | 0      |  |

| 1     | 0 | 0      |  |

| 1     | 1 | 1      |  |

|       |   |        |  |

(b)

Fig. 6. (a) Symbol of a traditional electronic AND gate. (b) Truth table of AND gate. (c) Transmission efficiency of the proposed all-optical AND logic gate at different input states.

Table 2 Operation of the proposed AND gate structure.

| State<br>of<br>input<br>port 1 | State<br>of<br>input<br>port 2 | Activation of input port 1 | Activation of input port 2 | Transmission efficiency | State<br>of<br>output<br>port | Activation of output port |

|--------------------------------|--------------------------------|----------------------------|----------------------------|-------------------------|-------------------------------|---------------------------|

| Logic 0                        | Logic<br>0                     | OFF                        | OFF                        | 0.73 %                  | Logic 0                       | OFF                       |

| Logic 0                        | Logic<br>1                     | OFF                        | ON                         | 0.82 %                  | Logic 0                       | OFF                       |

| Logic 1                        | Logic<br>0                     | ON                         | OFF                        | 0.82 %                  | Logic 0                       | OFF                       |

| Logic 1                        | Logic<br>1                     | ON                         | ON                         | 73%                     | Logic 1                       | ON                        |

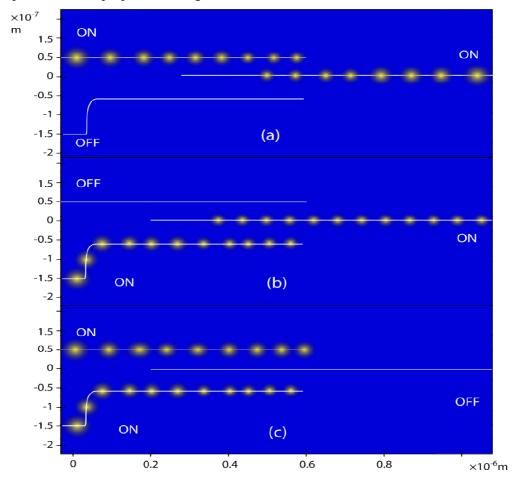

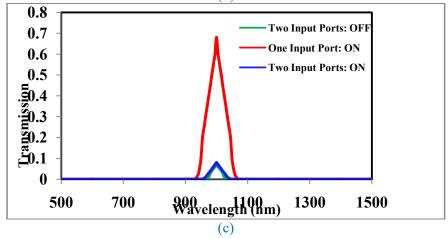

The same proposed interferometric structure in Fig. 1 can be used to obtain the function of XOR logic gate by employing the destructive interference between the two input ports caused by slight structure modification in input port 2 [XXIII]. Fig. 7demonstrates the distinction shape between graphene sheets, which is responsible for the destructive SSP mode coupling when both input ports are active (ON state). The transmission spectrum of the proposed XOR logic gate is shown in Fig. 8c. The operation of the proposed AND gate is summarized in Table 3.

Fig. 7. SPP mode distribution in the structure as XOR logic gate with  $\mu_{c} = 0.212$  eV,  $L_{c} = 346.75$  nm, and d = 50 nm. Input states: (a) only input port 1 is active, (b) only input port 2 is active, and (c) both input ports are active.

Copyright reserved © J. Mech. Cont.& Math. Sci. Hassan FalahFakhruldeen et al.

| Inp | Inputs |   |

|-----|--------|---|

| A   | В      | X |

| 0   | 0      | 0 |

| 0   | 1      | 1 |

| 1   | 0      | 1 |

| 1   | 1      | 0 |

|     | (b)    |   |

Fig. 8. (a) Symbol of a traditional electronic XOR gate. (b) Truth table of XOR gate. (c) Transmission efficiency of the proposed all-optical XOR logic gate at different input states.

**Table 3** Operation of the proposed XOR gate structure.

| State<br>of<br>input<br>port 1 | State<br>of<br>input<br>port 2 | Activation of input port 1 | Activation of input port 2 | Transmission efficiency | State<br>of<br>output<br>port | Activation of output port |

|--------------------------------|--------------------------------|----------------------------|----------------------------|-------------------------|-------------------------------|---------------------------|

| Logic 0                        | Logic<br>0                     | OFF                        | OFF                        | 0.65 %                  | Logic 0                       | OFF                       |

| Logic 0                        | Logic<br>1                     | OFF                        | ON                         | 68 %                    | Logic 1                       | ON                        |

| Logic 1                        | Logic<br>0                     | ON                         | OFF                        | 68 %                    | Logic 1                       | ON                        |

| Logic 1                        | Logic<br>1                     | ON                         | ON                         | 8 %                     | Logic 0                       | OFF                       |

#### IV. Conclusion

Three all-optical logic gates are proposed and implemented using the gates OR, AND, and XOR in this study. The proposed gates are structured using a graphene interferometric device with two input ports and one output port placed on silica substraight. Utilizing the functions of constructive and destructive interferences among the signals, modifying the coupling length  $L_c$  between the input and output ports with a straight property, changing the interspacing between the ports d, and

slightly tuning the chemical potential  $\mu_c$  of the plasmonic logic gates are achieved. The state of the output port (0 or 1) is determined on the basis of the transmission value through the port; if the transmission value is above the transmission threshold, which is assumed to be 0.5, then the state is 1; otherwise, the state is 0. Finally, the plasmonic gates are treated as fundamental parts in integrated photonic systems and all-optical signal-processing systems.

#### References

- I. A. F. Aguiar, D. M. d. C. Neves, and J. B. R. Silva, "All-optical logic gates devices based on SPP coupling between graphene sheets," *Journal of Microwaves, Optoelectronics and Electromagnetic Applications*, vol. 17, pp. 208-216, 2018.

- II. A. Vakil and N. Engheta, "Transformation optics using graphene," *Science*, vol. 332, pp. 1291-1294, 2011.

- III. B. Wang and G. P. Wang, "Surface plasmon polariton propagation in nanoscale metal gap waveguides," *Optics letters*, vol. 29, pp. 1992-1994, 2004.

- IV. D. A. Miller, "The role of optics in computing," *Nature Photonics*, vol. 4, p. 406, 2010.

- V. F. Wang, Y. Zhang, C. Tian, C. Girit, A. Zettl, M. Crommie, *et al.*, "Gate-variable optical transitions in graphene," *science*, vol. 320, pp. 206-209, 2008.

- VI. H. J. Caulfield and S. Dolev, "Why future supercomputing requires optics," *Nature Photonics*, vol. 4, p. 261, 2010.

- VII. H. J. Caulfield, C. S. Vikram, and A. Zavalin, "Optical logic redux," *Optik-International Journal for Light and Electron Optics*, vol. 117, pp. 199-209, 2006.

- VIII. H. Wei, Z. Wang, X. Tian, M. Käll, and H. Xu, "Cascaded logic gates in nanophotonic plasmon networks," *Nature communications*, vol. 2, p. 387, 2011.

- IX. Hassan Falah Fakhrulden and Tahreer Safa'a Mansour, "All-optical NoT Gate Based on Nanoring Silver-Air Plasmonic Waveguide," *International Journal of Engineering & Technology*, vol. 7, pp.2818-2821, 2018.

- X. K. J. Ooi, H. S. Chu, L. K. Ang, and P. Bai, "Mid-infrared active graphene nanoribbon plasmonic waveguide devices," *JOSA B*, vol. 30, pp. 3111-3116, 2013.

- XI. K. J. Ooi, H. S. Chu, P. Bai, and L. K. Ang, "Electro-optical graphene plasmonic logic gates," *Optics letters*, vol. 39, pp. 1629-1632, 2014.

#### J. Mech. Cont. & Math. Sci., Vol.-14, No.-5, September-October (2019) pp 98-110

- XII. M. Jablan, H. Buljan, and M. Soljačić, "Plasmonics in graphene at infrared frequencies," *Physical review B*, vol. 80, p. 245435, 2009.

- XIII. M. L. Brongersma and P. G. Kik, *Surface plasmon nanophotonics* vol. 131: Springer, 2007.

- XIV. M. W. McCutcheon, G. W. Rieger, J. F. Young, D. Dalacu, P. J. Poole, and R. L. Williams, "All-optical conditional logic with a nonlinear photonic crystal nanocavity," *Applied Physics Letters*, vol. 95, p. 221102, 2009.

- XV. M. Yarahmadi, M. K. Moravvej-Farshi, and L. Yousefi, "Subwavelength graphene-based plasmonic THz switches and logic gates," *IEEE Transactions on Terahertz Science and Technology*, vol. 5, pp. 725-731, 2015.

- XVI. optics," *nature*, vol. 424, p. 824, 2003.

- XVII. S. H. Abdulnabi and M. N. Abbas, "All-optical logic gates based on nanoring insulator-metal-insulator plasmonic waveguides at optical communications band," *Journal of Nanophotonics*, vol. 13, p. 016009, 2019.

- XVIII. S. I. Bozhevolnyi, V. S. Volkov, E. Devaux, J.-Y. Laluet, and T. W. Ebbesen, "Channel plasmon subwavelength waveguide components including interferometers and ring resonators," *Nature*, vol. 440, p. 508, 2006.

- XIX. X. Wu, J. Tian, and R. Yang, "A type of all-optical logic gate based on graphene surface plasmon polaritons," *Optics Communications*, vol. 403, pp. 185-192, 2017.

- XX. Y. Fu, X. Hu, C. Lu, S. Yue, H. Yang, and Q. Gong, "All-optical logic gates based on nanoscale plasmonic slot waveguides," *Nano letters*, vol. 12, pp. 5784-5790, 2012.

- XXI. Y. Liu, F. Qin, Z.-M. Meng, F. Zhou, Q.-H. Mao, and Z.-Y. Li, "All-optical logic gates based on two-dimensional low-refractive-index nonlinear photonic crystal slabs," *Optics express*, vol. 19, pp. 1945-1953, 2011.

- XXII. Yousif I. Hammadi and Tahreer S. Mansour., "Multiwavelength Erbium doped fiber laser based on microfiber Mach-Zehnder interferometer," Journal of Optoelectronics and Advanced Materials-Rapid Communications, vol.13, no.3-4, pp.156 160, April 2019.

- XXIII. Z. Li, E. A. Henriksen, Z. Jiang, Z. Hao, M. C. Martin, P. Kim, *et al.*, "Dirac charge dynamics in graphene by infrared spectroscopy," *Nature Physics*, vol. 4, p. 532, 2008.